Register Teil 2

Mit dem Eingangsteil aus Register Teil 1 und einem Tri-State-Buffer als Ausgang ist unsere Logik komplett.

Im Prinzip müssten wir jetzt 8x unsere bisherige Logik bauen und das Register wäre komplett.

Glücklicherweise gibt es hier fertige Bausteine, die uns die meiste Arbeit abnehmen, den 74XX273 (8-Fach Flip-Flop) und 74XX244 (8-Treiber mit Tristate-Ausgang).

Es gibt nur 3 kleine Fallstricke:

- die Steuereingänge für die Ausgänge am 74XX244 sind invertiert (0 = an, 1 = 0),

- es gibt keinen speziellen Aktivierungs-Eingang für das 74XX273,

- wir benötigen eine kleine Verzögerung, bevor wir unsere Daten einlesen, wir müssen den anderen Chips eine Chance geben, ihre Ausgänge zu aktivieren.

1. liesse sich, wie schon in Teil 1 beschrieben, durch ein einfaches UND-Eleement für den Clock-Eingang lösen.

2. Ein Inverter für den Ausgang-Enable Pin dreht das Signal um.

3. Wenn wir auf anstatt auf die steigende Flanke des CLK Signals reagieren, sondern auf die fallende Flanke, haben wir unsere Zeitverzögerung. Dazu müssten wir das CLK Signal durch einen Inverter jagen.

Das wären aber 2 ICs (2x Inverter + 2x AND).

Es lässt sich auch beides über ein NAND lösen.

Zur Erinnerung:

| A | B | Q |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Legen wir CLK und unseren Read-Eingang auf das NAND, haben wir bei Read=0 immer eine 1 am Ausgang, egal, was das CLK Signal macht. Bei Read=1 haben wir unseren Filter und gleichzeitig die Invertierung des CLK Signals.

Analog nehmen wir den Write Eingang und invertieren diesen durch ein Dauer-1 auf A.

Auch hier gibt es ein Element, das 74xx00.

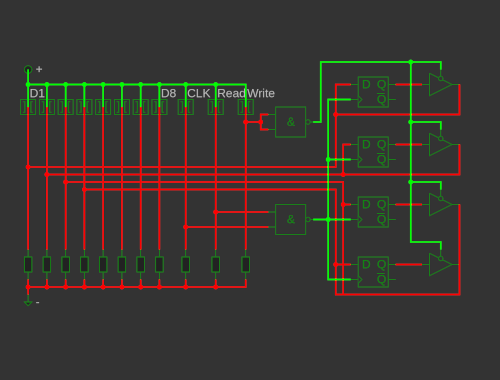

Das Gesamtbild (für die ersten 4 Bits) ergibt dann:

Am Ende haben wir ein 50% belegtes NAND 74x00, ein 8-Fach Flip-Flop 74xx273 und ein Treiber 74xx244 pro Register.

Als Breadboard mit 2 Registern sieht das dann so aus, wie in Computer Stufe 1