Register Teil 3

Basierend auf dem der letzten Runde "Register" und dem Konzept der ALU Registeradressierung, hier nun das vorläufig finale Bild des Registers mit ein paar "Extras".

Wir haben hier nun insgesamt 3 Busse:

- Allgemeine Datenbus

- Datenbus für ALU Register A

- Datenbus für ALU Register B

Wir können nun jeweils 16 Register an diesen Bus anschließen.

Das Freischalten der Registerinhalte auf den internen Datenbus erfolgt, wie bei anderen Modulen, über einen Tri-State Buffer, damit nur jeweils ein Register Daten auf die Leitungen gibt.

Wichtig: zum Spielen mit dem Simulator, schaltet in Vollbildmodus und zoomt rein (oben die Icons)

Das ist der obere Teil der Schaltung. Nun gibt es aber eine ganze Reihe an Magie auf der unteren Hälfte.

Basierend auf der Idee der Registeraddressierung gibt es nun ganz links eine Reihe von Jumpern, mit den auf dem Modul die Nummer des Registers eingestellt wird.

Diese Nummer wird für alle weiteren Logiken verwendet.

Die CPU-Steuerung (also aktuell der Mensch vor dem Simulator) hat nun eine ganze Menge Steuerleitungen zu bedienen.

Diese finden sich unten rechts auf den 3 Pin-Leisten.

Diese sind übrigens in der späteren Hardware über Flachbandkabel verbindbar. Diese werden dann später auf unsere Hauptplatine gesteckt So bildet sich ein Gebilde mit bis zu 16 Registern.

Auf diesen Steckern befindet sich nun die 3 Bus-Leitungen mit jeweils 8 Pins, die Read und Write Steuerleitung sowie jeweils 4x4 Register-Select Leitungen. Die sind für

- welches Register soll vom Datenbus lesen

- welches Register soll auf den Datenbus schreiben

- welches Register soll Daten auf ALU BUS A legen

- welches Register soll Daten auf ALU BUS B legen

Unten in der Mitte findet sich die Steuerlogik für diese Register-Select Leitungen.

Exemplarisch erklärt für das lesen vom Datenbus.

Die este Reihe von XNORs (Chip U6) vergleicht, ob die via Jumper ausgewählte (Teil-)Adresse der Registerauswahl dem von der Steuerung ausgewälten ID passt. Wenn dem so ist geht der Ausgang an.

Die 4 Bits werden über ein 4-Fach UND gesammengeführt. Wenn also alle Bits passen, gibt das OK.

Bei der Auswahl für lesen bzw. schreiben wird nun noch das lesen bzw. schreiben Signal von der Steuerung mitverbunden. Je nachdem ob wir ein "normales" oder invertiertes Signal brauchen über ein AND oder ein NAND.

Die Tri-State-Buffer wollen z.B. ein invertiertes Signal.

Auch aus praktischen Gründen (vermeidung eines Extra-IC) verwenden wir die freien NAND Element als NOT für die ALU-Bus Freigaben.

Für den Simulator gibt es nun die kleinen Rechtecke an den Pins, damit kann das Signal geändert werden. Jeweils ein Klick schalten an, aus und (z.B. bei den Datenleitungen) auch auf "unverbunden".

Damit kann das ganze Register durchgespielt werden.

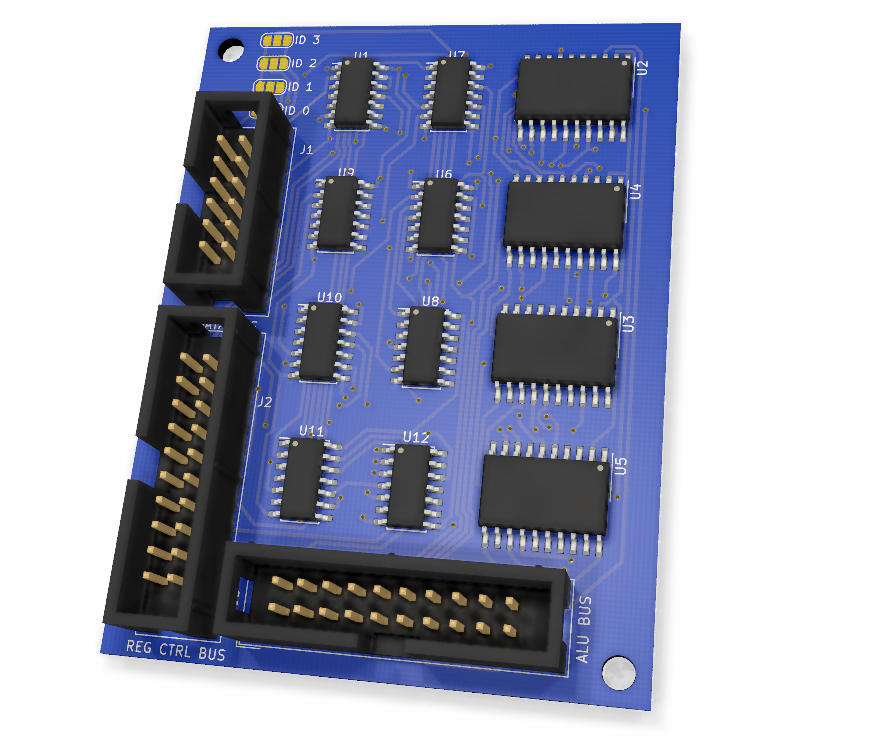

Dank des großartigen Tools KiCad hier eine Visualisierung, wie so ein Registermodul ausehen könnte (und evtl. wird):

Abmaße sind: ca. 57x75mm.

Und ja, das ist kompliziert. Wir bauen aber auch einen Computer, keinen Papier-Flieger.

Weiter geht es mit der Zusammenfassung der bisherigen Schritte als Blockschaltbild